用于COMe设计使用的官方规范,Rev3.0版本,绝对官方详细

”COMe 硬件设计“ 的搜索结果

PICMGCOM0R20COMe规范/COMe2.0规范spec

硬件电路设计基础(一).ppt

设计时将所使用到的片选信号 CSn 上拉,CSn0 上固定连接大 于 1MB 的 SPI NOR FLASH,用于存放 PMON。本文主要对龙芯2k1000设计做一个经验分享,大部分内容手册其实也都有,只是把一些关键的内容提取了出来,做一个...

PICMG_COM_0R3_0/ COMe Express R3.0/COMe 3.0 Spec(电子版非图片版)

RTC(Real_Time Clock)为整个电子系统提供时间基准,MCU、MPU、CPU均离不开RTC电路设计,在设计、应用RTC单元时,常常会发现延时、超时或者功耗过大现象,如何解决RTC精度以及功耗问题呢?本文将为您介绍时钟芯片PCF...

龙芯2K1000 PC评估板(面向移动智能终端)硬件资料包括官方设计的Cadence原理图+PCB+BOM文件,可供学习及设计参考。

类型COMexpressMINIType10(CompatibleType1)CPUIntelAtomN2600双核1.6G3.5WIntelAtomN2600双核1.86G6.5W芯片组IntelCG82NM10PCH内存DDR32GBonboard,256KBx8(-40——+85)存储8GBSSDNan...

硬件开发流程: 图1:硬件开发流程 图2:硬件开发流程简图 开发流程经验: ...

可惜资源分只有10分,这个资料是我在控创公司多轮交流之后才拿到的,为此...但作为注重开发和创新的硬件工程师,我又希望这个资源可以给每一位开发中的工程师提供帮助,希望你能在此基础上设计出更加完美的电路和产品。

硬件设计:POE--POE基础 参考资料:POE供电基础知识:PSE PD检测过程详解 POE供电简介 以太网供电 一、POE相关介绍 POE(Power Over Ethernet)是指在现有的以太网Cat.5布线基础架构上不做任何改动的情况下...

最近学习FPGA设计,学习了VGA驱动电脑显示屏的驱动方式、硬件设计、程序设计、数据转换工具设计等。主要包括VGA时序、驱动写入、数据处理等 一、VGA时序 1、VGA时序在网上有很多博客都写了其时序方式,在这里我...

基于国产飞腾、Intel X86等CPU主板设计与调试入门指导

可惜资源分只有10分,这个资料是我在EMERSON公司多轮交流之后才拿到的,...但作为注重开发和创新的硬件工程师,我又希望这个资源可以给每一位开发中的工程师提供帮助,希望你能在此基础上设计出更加完美的电路和产品。

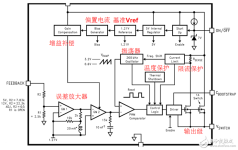

硬件设计:电源设计--倍压电路原理及应用 参考资料:简单直流二倍压电路介绍 倍压整流电路图大全(九款倍压整流电路设计原理图详解) 倍压整流电路的工作原理 在电路设计过程中,当后级需要的电压比前级高出...

硬件设计:逻辑电平--LVDS 参考资料:关于LVDS电平 LVDS电平 PECL、LVDS和CML电平 高速数字逻辑电平(8)之LVDS LVDS自学笔记 LVDS用户手册 LVDS和M-LVDS电路实施指南 LVDS(Low-Voltage Differential ...

1,单片机教程网 http://www.51hei.com/ 2,博客园 https://www.cnblogs.com/ 3,各种程序语言基础知识 https://www.runoob.com/cprogramming/c-scope-rules.html ...4,C语言中文网(基础教程) ...

硬件设计:元器件--二极管常用的七种用法 参考资料:https://wenku.baidu.com/view/5c3d8a5c804d2b160b4ec01d.html 二极管除单向导电特性外,还有许多特性,很多电路中并不是利用单向导电性就能分析二极管所...

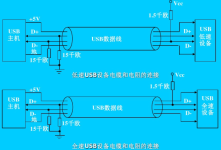

硬件设计:接口--不同电源系统下I2C总线电平转换电路(电桥)设计 参考资料:I2C总线3.3V与5V双向电平转换电路 为了实现在不同电源系统中通过I2C总线进行通讯,需要设计一种电平转换电路。 一、电路功能需求 ...

华为硬件开发小结 出处 “华为是怎样开发硬件的”——之一 1、文档、评审、设计 2、华为的流程 “华为是怎样开发硬件的”——之二 1、归一化 “华为是怎样开发硬件的”——之三 1、华为电路设计 ...

新一代硬件安全:第一章-简介

标签: 硬件工程

萤火学堂 视频:硬件设计-PCB原理图简要讲解 https://v.youku.com/v_show/id_XNDY0MTYyNDk4NA%3D%3D.html

4.设计要留有余量,避免电源芯片过热,攻耗达到额定值的50%要用散热片。 二、输入IO记得要上拉; 三、输出IO记得核算驱动能力; 四、高速IO,布线过长采用33殴电阻抑制反射; 五、各芯片之间电平匹配; 六、...

推荐文章

- 记录nvm use node.js版本失败,出现报错: exit status 1: ��û���㹻��Ȩ��ִ�д˲�����_nvm use失败-程序员宅基地

- lua面向对象编程之点号与冒号的差异详细比较-程序员宅基地

- 百度云虚假下载_虚假新闻:关于公共云的5种常见误解-程序员宅基地

- Tesseract图像识别OCR的学习1_tesseract doocr-程序员宅基地

- 不同层级的Android开发者的不同行为,我们该如何进阶和规划?-程序员宅基地

- Pelee: A real-time object detection system on mobile devices-程序员宅基地

- Hadoop环境搭建(保姆级教学)_hadoop平台搭建步骤-程序员宅基地

- ZooKeeper实战之ZkClient客户端实现负载均衡_zookeeper实现负载均衡案例-程序员宅基地

- Android 枚举 VS 枚举注解_android 枚举注解-程序员宅基地

- HDU1715--第i个斐波那契数 大菲波数_返回第i个斐波那契数-程序员宅基地